2023/08/11 第十五集

处理器内核和存储空间映射

内部结构

24位地址总线 16M存储器

无需外部flash总线

结构和地址空间

MOVC MOVS 人为增加了指令的复杂度

24位总线引入段的概念,直接知道访问的十哪一片区域

64k程序空间

code

64k程序空间 code区域 程序代码FF:0000H 到FF:FFFFH

ecode ecode 拓展

保留 留着以后研发芯片,给与新的用途

64k拓展RAM 外部扩展SRAM 用的地址,试验箱有没焊接,只支持8位数据

拓展SFR 不是传统SFR,传统SFR还保留

保留 很大 留着以后用

8K 扩展RAM 扩展ram 也是在cpu内部

xdata 也不是随便分,intel有个基本的规则

保留 64K edata SRAM越大性能越高也越贵

速度快

4kRAM

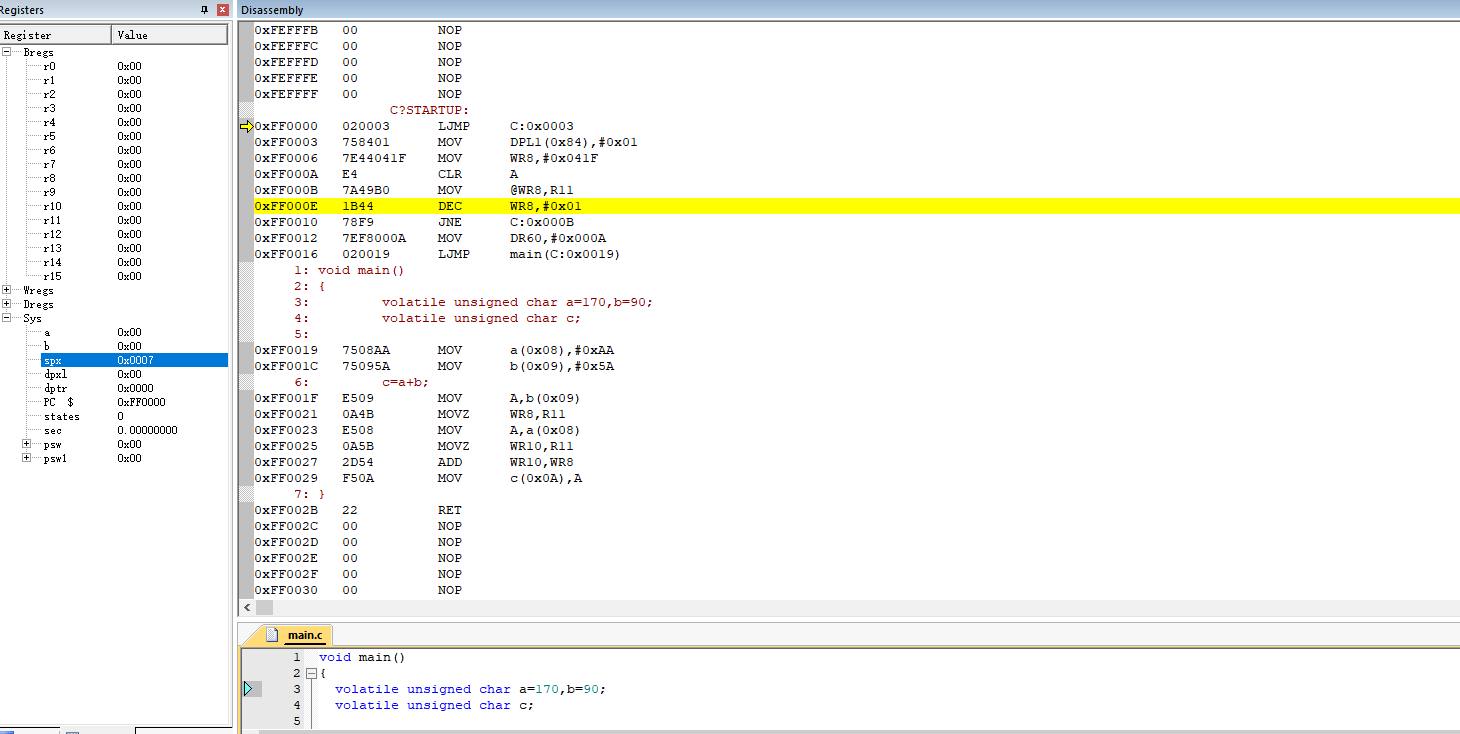

一段简单的测试代码

- void main()

- {

- volatile unsigned char a=170,b=90;

- volatile unsigned char c;

-

- c=a+b;

- }

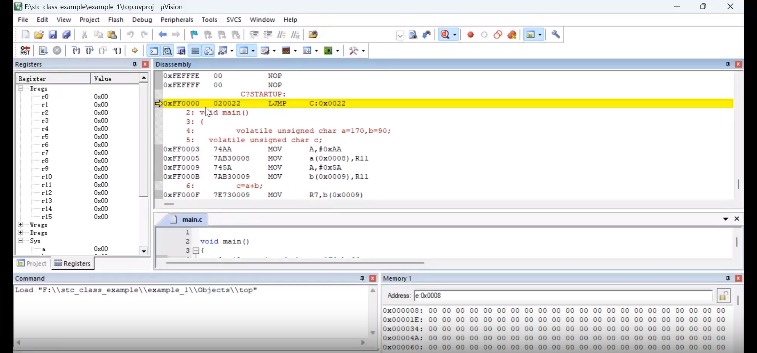

取消run to main()调试

好奇为啥我这里的启动引导代码与何老师的不一样,我这里不是一个简单的跳转指令,

先是移动了一下dptr,然后向寄存器里面放了个立即数0x41f ,再进行自减运算

减到0后才进行跳转

没问题了,何老师的启动引导代码再后面0xFF0022那里,是一样的

下面是何老师的启动引导代码

00:0000~00:0FFF 基本RAM

4K EDATA

7E:0000~7E:FFFF XSFR

拓展sfr,能访问更多的设备,原来的sfr不够用了。

复位PC 从FF:0000H 开始

中断PC 从对应的中断入口开始

FF:0003H INT0中断

eeprom 扇区擦除

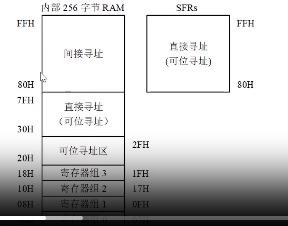

低端256字节RAM

这里兼容传统8051

stc32g RAM 12K

4K EDATA

8K XDATA(理论能到8MB)

可位寻址存储器

DATA 0x20~0x7F

96字节

SFR 0x80~0xFF (原来传统8051是被8整除)

128字节

中断

stc32展现工程能力创新,实践能力创新

中断机制与arm有一些不同

最快相应,最小代价。

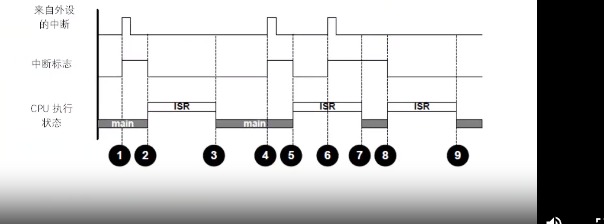

中断原理

正在执行某个事件,外部紧急事件

cpu轮询<中断<DMA

RX ______________

------> | 移位接收缓存器 |

|高电平通知cpu |

| cpu |

|_______________|

cpu 检测高电平/脉冲 响应根源

如果不响应,缓冲区溢出,产生错误

中断优先级有程序设计人员决定

高低电平 还是脉冲由芯片设计人员决定(看数据手册)

中断标志

在寄存器中。在早期轮询系统中,轮询寄存器中标志位,判断是否发生中断。

发生中断,停止main函数的执行。执行中断子程序,执行结束,恢复main函数

堆栈机制用于中断前地址的存储

中断系统

实现中断过程的功能部件

中断源

打断当前执行程序的紧急时间

中断优先级

多个中断,优先处理 优先级高的(先和校长说话)。

|  |手机版|深圳国芯人工智能有限公司

( 粤ICP备2022108929号-2 )

|手机版|深圳国芯人工智能有限公司

( 粤ICP备2022108929号-2 )