|

|

发表于 2024-12-27 16:22:19

|

显示全部楼层

发表于 2024-12-27 16:22:19

|

显示全部楼层

这份代码试了试,目前结果是这样的。

由于我手里没有开发板,只有公司成品。目前成品的SPI是用的P1.2 P1.3 P1.4 P1.5 引脚。所以我把这里边的代码SPI引脚使用部分做了下改动,具体改动如下:

主机程序:

void SPI_init(void)

{

SPI_SS = 1;

SPCTL = 0xd4; //使能 SPI 主机模式进行待机

// AUXR1 = (AUXR1 & ~(3<<2)) | (1<<2); //IO口切换. 0: P1.2/P5.4 P1.3 P1.4 P1.5, 1: P2.2 P2.3 P2.4 P2.5, 2: P7.4 P7.5 P7.6 P7.7, 3: P3.5 P3.4 P3.3 P3.2

AUXR1 = (AUXR1 & ~(3<<2)) ; //IO口切换. 0: P1.2/P5.4 P1.3 P1.4 P1.5, 1: P2.2 P2.3 P2.4 P2.5, 2: P7.4 P7.5 P7.6 P7.7, 3: P3.5 P3.4 P3.3 P3.2

IE2 |= ESPI; //使能 SPI 中断

SPSTAT = SPIF + WCOL; //清0 SPIF和WCOL标志

SPI_TimeOut = 0;

B_SPI_Busy = 0;

SPI_Cnt = 0;

}

从机程序:

void SPI_init(void)

{

SPI_SS = 1;

SPCTL = 0x44; //使能 SPI 从机模式进行待机

// AUXR1 = (AUXR1 & ~(3<<2)) | (1<<2); //IO口切换. 0: P1.2/P5.4 P1.3 P1.4 P1.5, 1: P2.2 P2.3 P2.4 P2.5, 2: P7.4 P7.5 P7.6 P7.7, 3: P3.5 P3.4 P3.3 P3.2

AUXR1 = (AUXR1 & ~(3<<2)); //IO口切换. 0: P1.2/P5.4 P1.3 P1.4 P1.5, 1: P2.2 P2.3 P2.4 P2.5, 2: P7.4 P7.5 P7.6 P7.7, 3: P3.5 P3.4 P3.3 P3.2

IE2 |= ESPI; //使能 SPI 中断

SPSTAT = SPIF + WCOL; //清0 SPIF和WCOL标志

SPDAT = 0x55; //设置回复的第一个字节数据

SPI_TimeOut = 0;

B_SPI_Busy = 0;

B_SPI_Send = 0;

SPI_Cnt = 0;

}

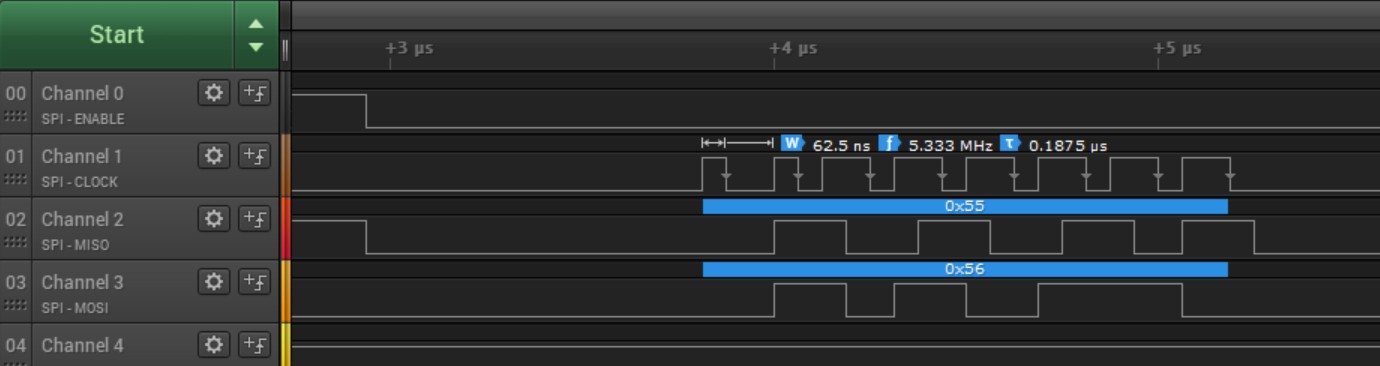

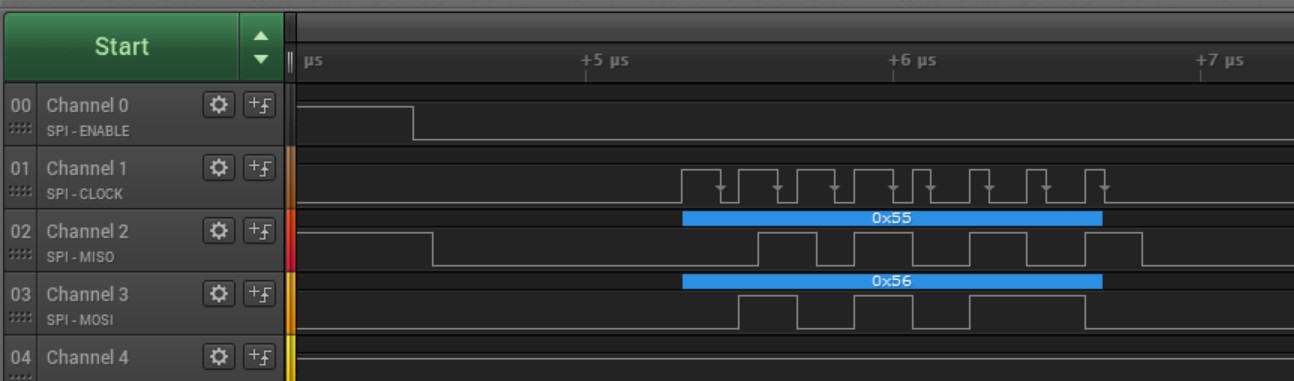

这样将两份程序分别下进去后,然后通过主机的串口一直发送数据0x56,从机会返回0x55,我通过逻辑分析仪抓到的波形如下:

可以看到这个时钟的波形不太规整,主机程序控制的MOSI引脚是在上升沿产生变化的,而从机控制的MISO引脚是有的时候在上升沿有的时候在上升沿过一点。

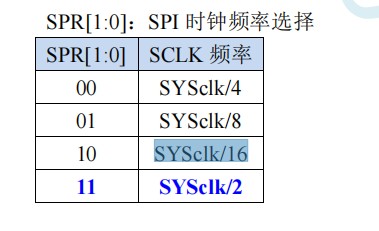

这个时候我怀疑是不是这个SPI速率太快导致从机反应没那么快的问题导致的,于是我将主机和从机代码的SPI速率都设置为SYSclk/16

主机程序:

void SPI_init(void)

{

SPI_SS = 1;

// SPCTL = 0xd4; //使能 SPI 主机模式进行待机

SPCTL = 0xd6; //使能 SPI 主机模式进行待机

// AUXR1 = (AUXR1 & ~(3<<2)) | (1<<2); //IO口切换. 0: P1.2/P5.4 P1.3 P1.4 P1.5, 1: P2.2 P2.3 P2.4 P2.5, 2: P7.4 P7.5 P7.6 P7.7, 3: P3.5 P3.4 P3.3 P3.2

AUXR1 = (AUXR1 & ~(3<<2)) ; //IO口切换. 0: P1.2/P5.4 P1.3 P1.4 P1.5, 1: P2.2 P2.3 P2.4 P2.5, 2: P7.4 P7.5 P7.6 P7.7, 3: P3.5 P3.4 P3.3 P3.2

IE2 |= ESPI; //使能 SPI 中断

SPSTAT = SPIF + WCOL; //清0 SPIF和WCOL标志

SPI_TimeOut = 0;

B_SPI_Busy = 0;

SPI_Cnt = 0;

}

从机程序:

void SPI_init(void)

{

SPI_SS = 1;

// SPCTL = 0x44; //使能 SPI 从机模式进行待机

SPCTL = 0x46; //使能 SPI 从机模式进行待机

// AUXR1 = (AUXR1 & ~(3<<2)) | (1<<2); //IO口切换. 0: P1.2/P5.4 P1.3 P1.4 P1.5, 1: P2.2 P2.3 P2.4 P2.5, 2: P7.4 P7.5 P7.6 P7.7, 3: P3.5 P3.4 P3.3 P3.2

AUXR1 = (AUXR1 & ~(3<<2)); //IO口切换. 0: P1.2/P5.4 P1.3 P1.4 P1.5, 1: P2.2 P2.3 P2.4 P2.5, 2: P7.4 P7.5 P7.6 P7.7, 3: P3.5 P3.4 P3.3 P3.2

IE2 |= ESPI; //使能 SPI 中断

SPSTAT = SPIF + WCOL; //清0 SPIF和WCOL标志

SPDAT = 0x55; //设置回复的第一个字节数据

SPI_TimeOut = 0;

B_SPI_Busy = 0;

B_SPI_Send = 0;

SPI_Cnt = 0;

}

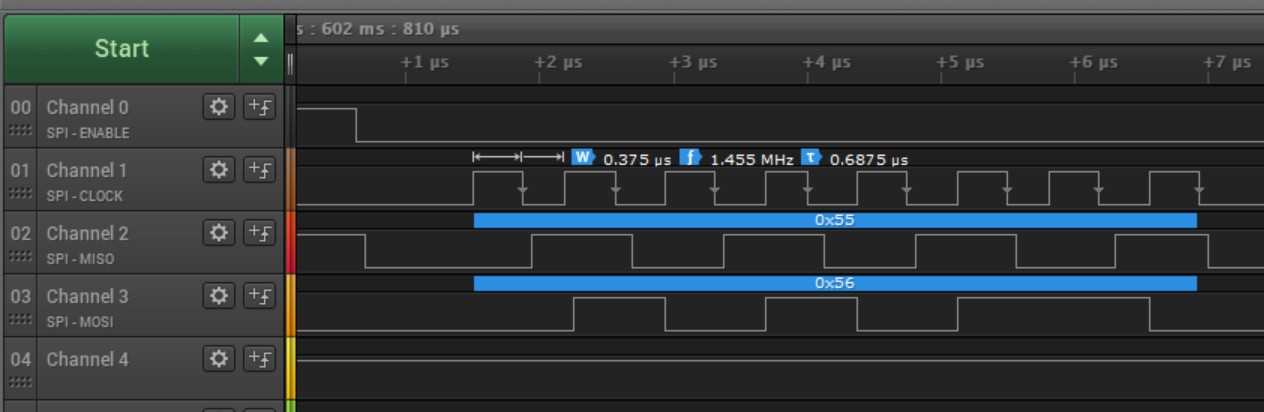

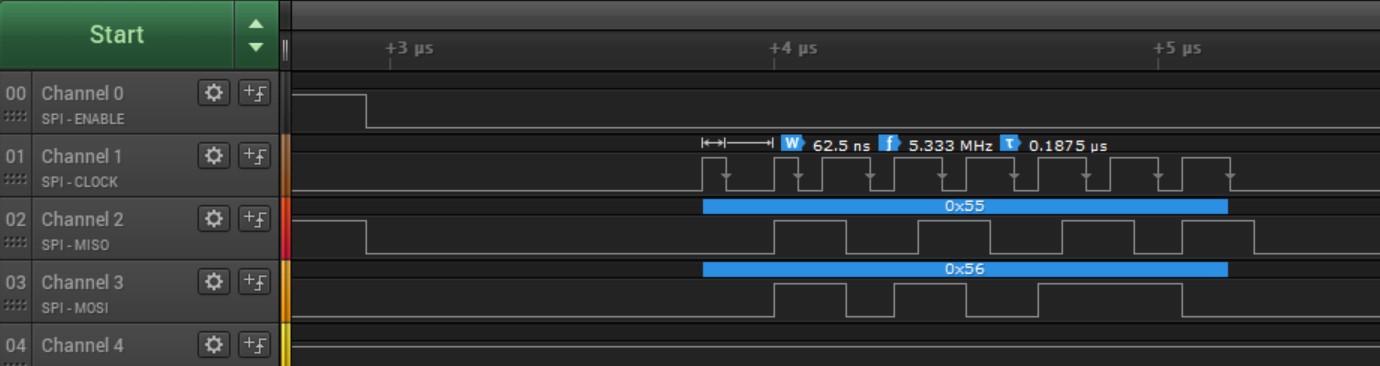

还是主机通过串口发送0x56,通过逻辑分析仪抓到的波形如下:

此时可以看到主机的mosi引脚都是在上升沿变化的,而从机的MISO引脚是在下降沿过了一点点变化的。

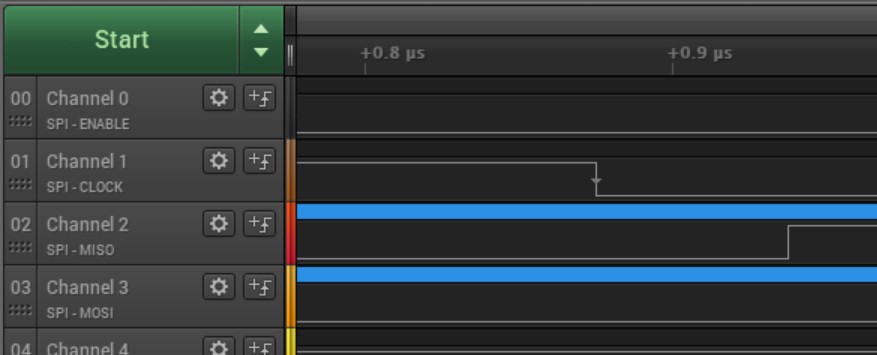

放大下降沿的时候改变miso引脚部分如下:

可以看到此时现象与我一开始反馈现象一致,都是在采集沿过了不到0.1us就产生了变化。

|

-

-

|

|手机版|深圳国芯人工智能有限公司

( 粤ICP备2022108929号-2 )

|手机版|深圳国芯人工智能有限公司

( 粤ICP备2022108929号-2 )