- 打卡等级:偶尔看看III

- 打卡总天数:40

- 最近打卡:2025-10-28 01:41:37

金牌会员

- 积分

- 1218

|

部分MCU资料可以看到说明,可以配置为双缓冲,以最大化吞吐率。

一个缓冲区在CPU处理数据时,USB使用另一个缓冲区传输数据。

USB的缓冲区可寻址,可由CPU直接访问。

而STC的USB和那些不一样,USB部分和CPU部分之间由一个异步FIFO连接。

这样做的好处显而易见,两者可以采用各自独立的时钟。

USB作为独立外设时钟48MHz是固定不能变的,

而MCU其它部分可以采用任意其它频率,

比如 45MHz, 44.2368MHz, 40MHz, 36.864MHz,

33.1776MHz, 24MHz, 22.1184MHz,12MHz, 11.0592MHz, 等灵活的较低频率。

这样功耗低,电磁辐射小。

看了STC的资料,有些地方不明白,FIFO能否容纳多个数据包?

即收到一个数据包,尚未处理,未清空FIFO时,

上位机再次发来一个OUT包,能否接受?

IN的处理同理。

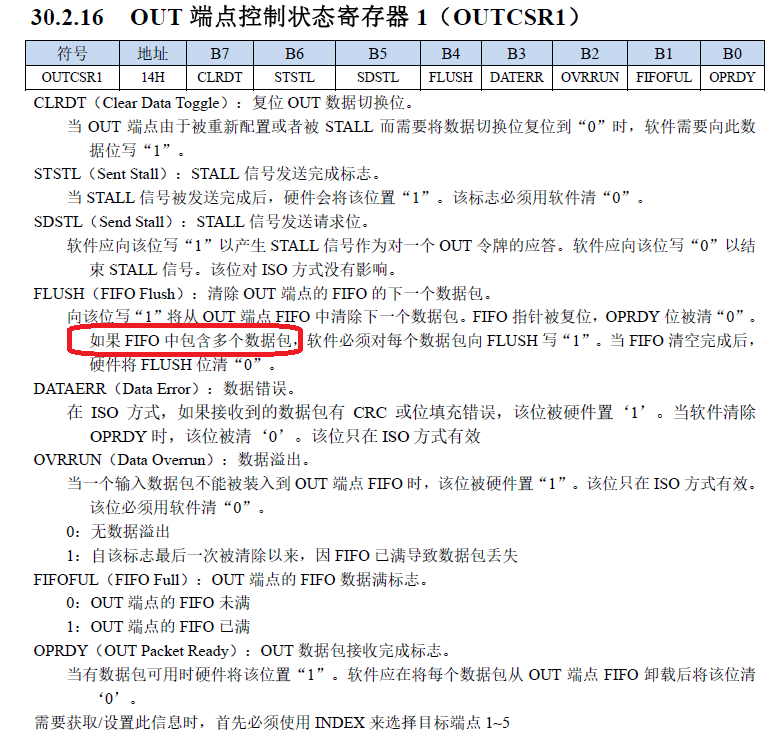

数据手册中提了一句,FIFO中可以包含多个数据包,但是没有详细的说明。

按照提供的例程的处理逻辑,

收到OUT数据包,产生中断,读取收到数据包字节数,

从FIFO逐个字节读取并复制到一个缓冲区,清除OPRDY标志。

经实际测试,在清空FIFO清除OPRDY标志前,上位机发送OUT包是不成功的,会NAK。

直到OPRDY标志清除后,才可以成功发送下一包。

类似多包连发或其它MCU双缓冲这种效果能实现吗?

|

|

|手机版|深圳国芯人工智能有限公司

( 粤ICP备2022108929号-2 )

|手机版|深圳国芯人工智能有限公司

( 粤ICP备2022108929号-2 )