- жү“еҚЎзӯүзә§пјҡеҒ¶е°”зңӢзңӢIII

- жү“еҚЎжҖ»еӨ©ж•°пјҡ30

- жңҖиҝ‘жү“еҚЎпјҡ2025-06-23 08:41:18

е·Із»‘е®ҡжүӢжңә е·Із»‘е®ҡжүӢжңәдёӯзә§дјҡе‘ҳ

- з§ҜеҲҶ

- 474

|

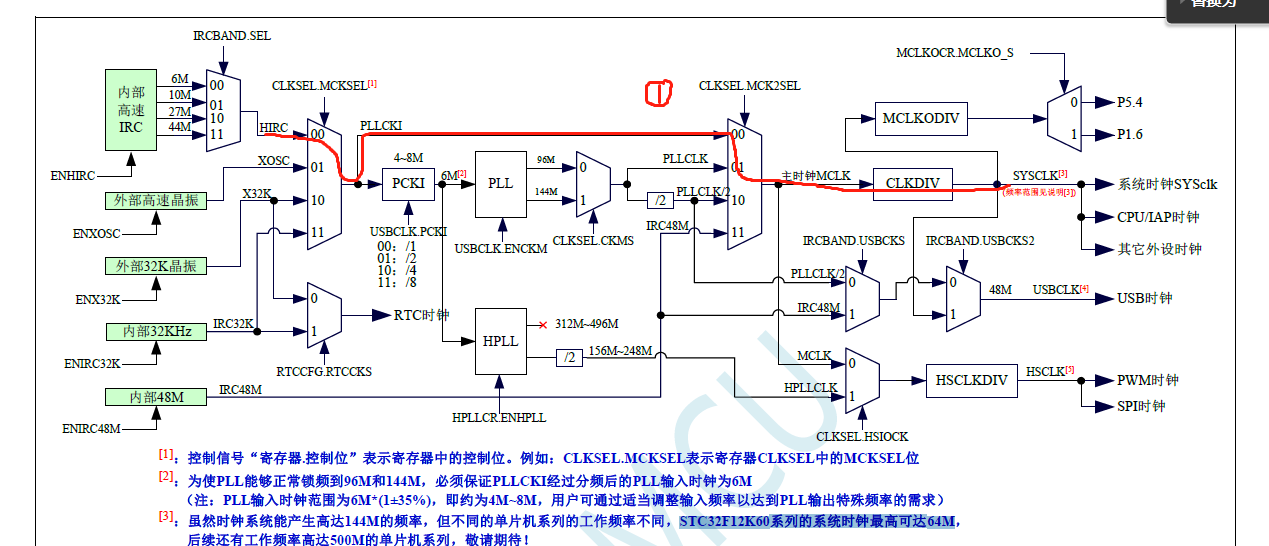

е…ідәҺ32Fж—¶й’ҹзҡ„йҖүжӢ©й—®йўҳпјҢеҰӮжһңжҲ‘жғізі»з»ҹж—¶й’ҹSYSCLKдёә60M,жҲ‘е°ұеҸҜд»Ҙиө°1еҸ·и·Ҝзәҝе®һзҺ°пјҢеҰӮдёӢеӣҫпјҡ

йӮЈжҲ‘еҰӮжһңдҪҝз”ЁеӨ–йғЁж—¶й’ҹдҪңдёәж—¶й’ҹжәҗеҗҢж ·жғізі»з»ҹж—¶й’ҹSYSCLKдёә60MпјҢжҲ‘жҷ¶жҢҜйў‘зҺҮеә”иҜҘйҖүеӨҡеӨ§зҡ„пјҢ6M,12M,иҝҳжҳҜ24M(еҸӘиҰҒPCKIиҫ“еҮәж»Ўи¶і6Mе°ұиЎҢд№Ҳ)?

з»ҸиҝҮPCKI,PLL,CLKSELжңҖз»Ҳзҡ„е§Ӣз»ҲжҳҜеӨҡе°‘?жҲ‘зңӢж—¶й’ҹз®ЎзҗҶзҜҮдёӢиҫ№и§ЈйҮҠиҜҙжҳҜжңҖеӨ§64M,еӣ дёәPLLиҫ“еҮәиҰҒд№Ҳ96,144жҲ–иҖ…他们зҡ„2еҲҶйў‘пјҢйӮЈеҗҺиҫ№SYSCLKжңҖеӨ§д№ҹе°ұжҳҜ48MпјҢдёҚзҹҘйҒ“жҲ‘зҗҶи§Јзҡ„еҜ№дёҚеҜ№пјҹ

|

|

|жүӢжңәзүҲ|ж·ұеңіеӣҪиҠҜдәәе·ҘжҷәиғҪжңүйҷҗе…¬еҸё

( зІӨICPеӨҮ2022108929еҸ·-2 )

|жүӢжңәзүҲ|ж·ұеңіеӣҪиҠҜдәәе·ҘжҷәиғҪжңүйҷҗе…¬еҸё

( зІӨICPеӨҮ2022108929еҸ·-2 )